TR10a-LP QDRII + Arria 10 FPGA開発キット

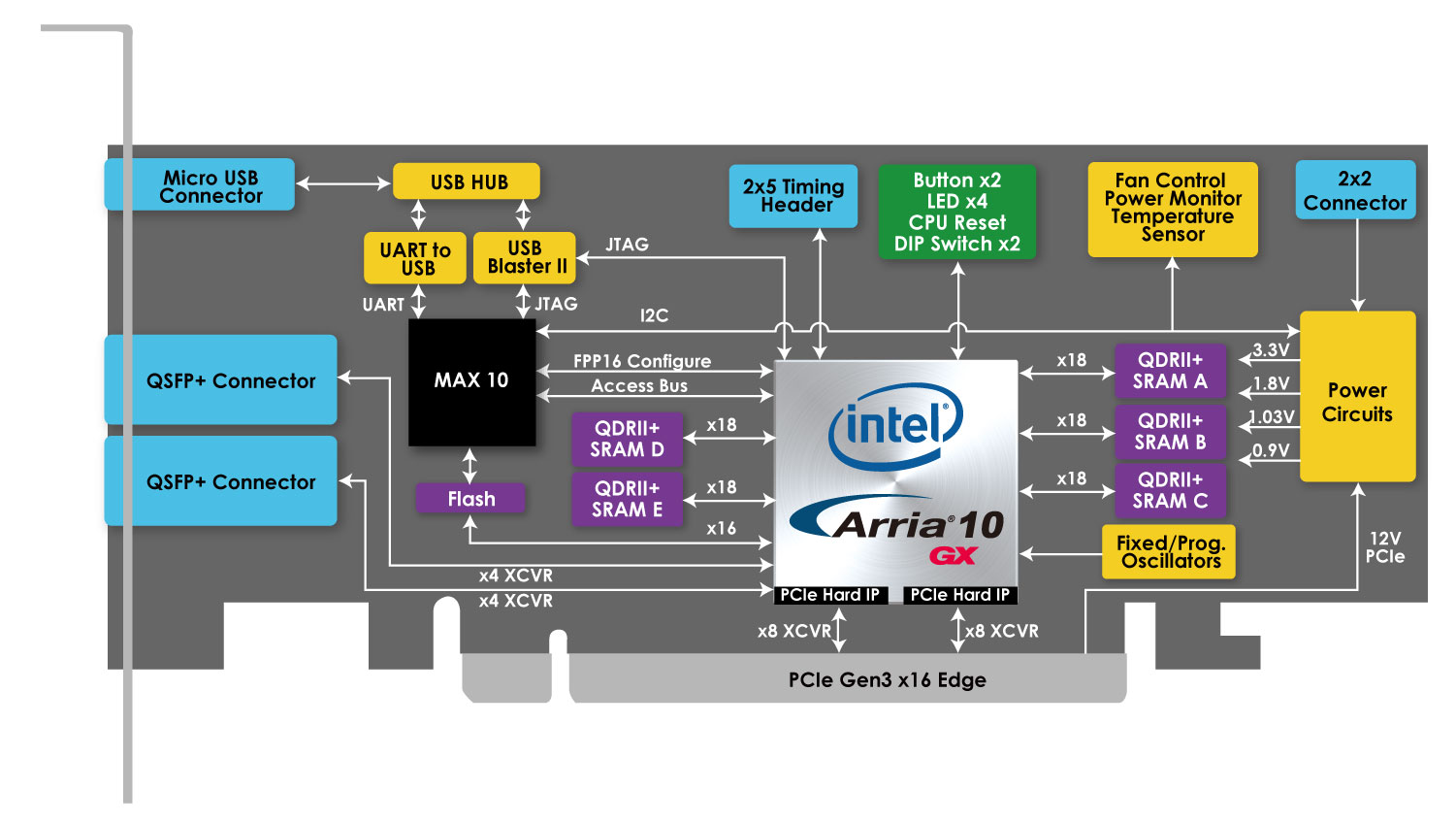

AI、データセンター、および高周波取引の要求にインスパイアされたTerasicのTR10a-LPQ(DDR4)は、次世代の高性能システムの要求に対応するための高速化および高速接続アプリケーション向けに設計されています。

TR10a-LPQはPCI Express規格のバージョン3.0に完全に準拠しており、2つの外部40G QSFP +モジュールへの超低遅延のストレート接続をサポートします。 QDRII + SRAM、高速パラレルフラッシュメモリの5つのポートも含まれています。

Terasicは、大手IPプロバイダと提携して、金融、ネットワーキング、およびさまざまな高速接続アプリケーションに最先端のソリューションを提供しています。

| |  |

| アルゴロジック | | エニックス |

ターゲット市場:

| |  | |  | |  | |

|

| 高周波取引 | | 高性能コンピューティング | | データセンター | | ミリタリーと航空宇宙 | | 5Gコネクティビティ |

コンポーネントパートナー

| |  | |  |

| 電源ソリューション | | X2Yパワーデカップリングソリューション | | SRAMソリューション |

| | | | |

| |  | |  |

| 容量性部品ソリューション | | クロックソリューション | | 誘導部品ソリューション |

FPGA

- Intel Arria 10 GX FPGA(10AX115N2F45E1SG)

FPGAコンフィギュレーション

- FPGAプログラミング用のオンボードUSB Blaster II

- FPPx16構成用1GビットCFIフラッシュ

記憶

- 5つの独立した550メガヘルツQDRII、18ビットデータバスおよびそれぞれのための72Mbit(最高288Mbit)

(DDR4メモリバージョンも利用可能です。Terasicセールスチームにお問い合わせください。)

コミュニケーションと拡大

- PCIeロープロファイルフォームファクタ

- PCIe x 16エッジコネクタ(デュアルPC 3世代x 8インターフェイスを含む)

- 2つの40G QSFP +外部モジュールへの超低遅延のストレート接続を可能にします

- ボード管理用のUART to USB

- 1ppsまたは他の高精度クロック入力用の2x5タイミング拡張ヘッダー付き

その他

- ユーザーLED×4、ボタン×2、スイッチ×2

- 固定周波数OSCおよびプログラマブルクロックジェネレータ

- 電源モニタ、温度モニタ、ファン制御。

書類

| タイトル | バージョン | サイズ(KB) | 追加日 | ダウンロード |

|---|

| TR10a-LPQの取扱説明書 | 1.1.0 | 8557 | 2019-04-18 |  |

CD-ROM

| タイトル | バージョン | サイズ(KB) | 追加日 | ダウンロード |

|---|

| TR10a-LPQ CD-ROM | 1.0.1 | | 2019-04-18 | |